# **Shared Learning**

SL028/18 – Control Table Error

## **Background**

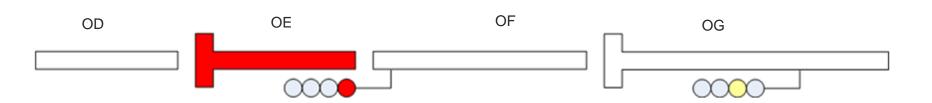

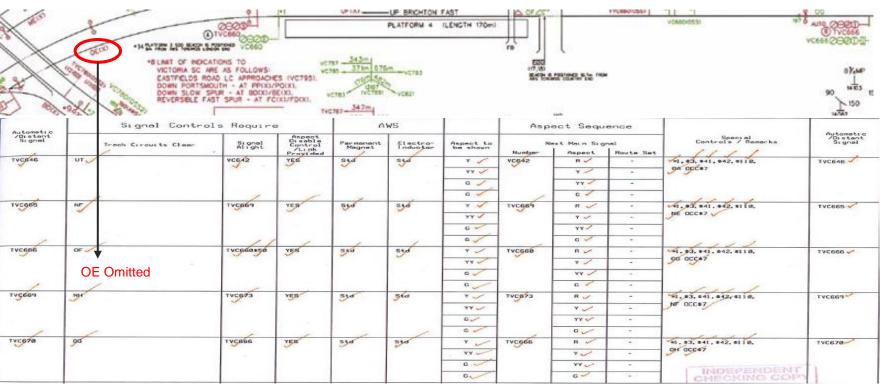

A separate overlap track on an auto-signal got omitted from the control tables.

The error in the control tables was not spotted anywhere in the checking, data design or testing processes, with the issue ultimately being identified by the Signaller post commissioning.

Although this was a very simple arrangement, the presentation of the information on the scheme plan, in the control tables and the mentoring arrangements for the design staff appear to have contributed to the overlap being omitted.

#### Control Table Error

This signal was the only auto-signal with a separate overlap section on that sheet in the control tables. Therefore the control table sheet had a uniform appearance and the omission of the separate overlap section was not apparent.

## Scheme Plan Presentation

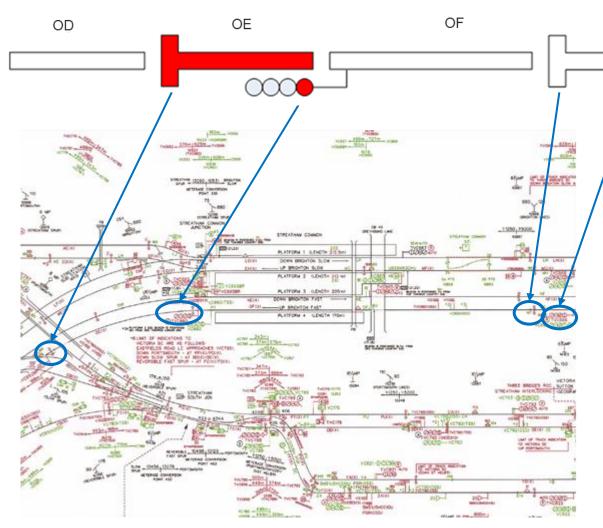

A change of scale, along with the presence of the overbridge and junction mean that the omitted overlap joint is more difficult to locate & associate with the signal.

OG

## Mentoring & Paused Design

- The initial control table design was paused for a number of months and when restarted was picked up by a different designer working under mentorship.

- Although it was understood that the initial control table design was both unfinished and unchecked; it appears that an error in this initial draft was perpetuated throughout the project life.

- Staff were under mentorship in a number of different roles throughout the project process. Application of mentoring processes, the understanding of mentor responsibilities and the time made available for mentors to discharge their duties varied significantly.

#### Lessons Learnt

- Many of the new data tools designed to support the design verifiers and testers, use the control tables as their source data; consequently an error in the control tables could pass through these systems undetected.

- At all points in the design, install and test processes queries should be referenced back to source documents; including scheme plan and requirements documents; to ensure no over-reliance on a single design document.

- Mentors and Mentees must each be clear about their responsibilities and be able to devote sufficient time to discharge these.

- The CEM needs to clearly understand and assess the impact of mentoring arrangements on the collective capability of the team deployed and any additionality that is introduced by having multiple layers of mentorship across functions, e.g. design, install, test.

## Further Learning

- Projects should put in place robust processes for both pausing and restarting project work, to improve management and control of designs. Consideration should be given to changes of project staff and how information will be communicated.

- Work to simplify / declutter scheme plans for Data Designers & Principles Testers is underway. However, until this is implemented Designers are reminded to think about the end users of their designs to ensure the information they present is as clear as possible.

## **Further Information**

For any further details or information please contact:

Nicola Crocker, Programme Engineering Manager, Process & Capability

07733127167

Nicola.Crocker@networkrail.co.uk